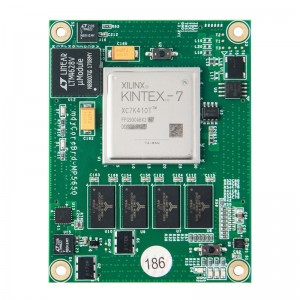

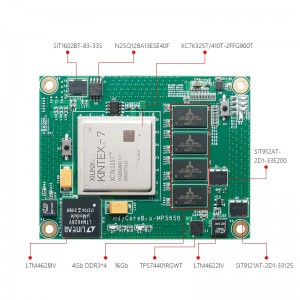

FPGA XILINX-K7 KINTEX7 XC7K325 410T Industria grado

DDR3 SDRAMQ: 16GB DDR3, 4GB po peco, 16-bita Datenbita Daten-Oferto SPI-Fulmo: Unu peco de 128MBITQSPIFULMO, uzebla por FPGA-agordodosieroj kaj uzantodatumoj. Interfacaj niveloj de FPGA-banko: agordeblaj 1.8V, 2.5V, 3.3V elektraj. Se vi bezonas anstataŭigi la nivelon, vi nur bezonas anstataŭigi la respondan pozicion de la magneta globeto por atingi la alĝustigon. Nutrado de la kerna plato: EEPROM-nutrado kun gamo 5V-12V; M24C02-WMN6TP baziĝas sur I2C-busa aparato. Sekvante la startmetodon de la kerna plato, la dua-linia protokolo: subtenas du startreĝimojn, kiuj estas JTAG kaj QSPI-fulmkonektiloj. Plilongigita pordo, 120-pingla, Panasonic AXK5A2137yg MP5700 funda plato SFP-interfaco: 2 optikaj moduloj povas atingi altrapidan optikfibran komunikadon, ĝis 6GB/s. Funda plato-horloĝo: 1 200MHz referenca horloĝo konektita al la kerna plato. MRCC-horloĝa tubpiedo, 1 125MHz. La GTX-horloĝa tubpiedo, la funda plato de la horloĝo konektita al la kerna plato, estas 40-pingla etenda pordo: rezervas 2,54mm norman interspacigan 40-pinglan etendan pordon, kiu estas uzata por konekti la propran dezajnan modulon de la kliento. Essence Kerna plato-horloĝo: ekzistas pluraj horloĝfontoj sur la plato. Ĉi tiuj inkluzivas la 200MHz sisteman horloĝon, la 125MHz GTX-horloĝon, kaj la 66MHz EMCCLK-horloĝon. JTAG-pordo: 10 kudreroj 2,54mm norma JTAG-pordo, por elŝuti kaj sencimigi LED-ojn por FPGA-programoj: entute 6 ruĝaj LED-lumoj en la kerna plato, indikante la elektroprovizon de la plato, 4 signalindikiloj kaj FPGA-IO-tubpiedoj rekte konektitaj. Ŝlosilo: 4 klavoj. 4 klavoj. Ili estas FPGA-rekomencigbutonoj, Program_b-klavoj kaj du uzanto-klavoj.

La FPGA Xilinx-K7 Kintex7 XC7K325 410T estas specifa modelo de FPGA (Field-Programmable Gate Array - Kampe Programebla Pordega Aro) disvolvita de Xilinx. Jen kelkaj ŝlosilaj detaloj pri ĉi tiu FPGA: Serio: Kintex-7: La Kintex-7 serio FPGA-oj de Xilinx estas desegnitaj por alt-efikecaj aplikoj kaj ofertas bonan ekvilibron inter efikeco, potenco kaj prezo. Aparato: XC7K325: Ĉi tio rilatas al la specifa aparato ene de la Kintex-7 serio. La XC7K325 estas unu el la variaĵoj haveblaj en ĉi tiu serio, kaj ĝi ofertas certajn specifojn, inkluzive de logika ĉelkapacito, DSP-tranĉaĵoj kaj I/O-kalkulo. Logika Kapacito: La XC7K325 havas logikan ĉelkapaciton de 325 000. Logikaj ĉeloj estas programeblaj konstrubriketoj en FPGA, kiuj povas esti agorditaj por efektivigi ciferecajn cirkvitojn kaj funkciojn. DSP-tranĉaĵoj: DSP-tranĉaĵoj estas dediĉitaj aparataraj rimedoj ene de FPGA, kiuj estas optimumigitaj por ciferecaj signal-prilaboraj taskoj. La preciza nombro de DSP-tranĉaĵoj en la XC7K325 povas varii depende de la specifa variaĵo. I/O-kalkulo: La "410T" en la modelnumero indikas, ke la XC7K325 havas entute 410 uzantajn I/O-pinglojn. Ĉi tiuj pingloj povas esti uzataj por interagi kun eksteraj aparatoj aŭ aliaj ciferecaj cirkvitoj. Aliaj Trajtoj: La XC7K325 FPGA povas havi aliajn funkciojn, kiel ekzemple integrajn memorblokojn (BRAM), altrapidajn ricevilojn por datenkomunikado kaj diversajn konfiguraciajn opciojn. Gravas noti, ke FPGA-oj kiel la Xilinx-K7 Kintex7 XC7K325 estas programeblaj aparatoj, kiuj permesas al vi efektivigi kutimajn ciferecajn cirkvitojn kaj funkciojn programante iliajn logikajn ĉelojn. Ĉi tiu fleksebleco igas ilin taŭgaj por vasta gamo da aplikoj, inkluzive de alt-efikeca komputado, cifereca signalprilaborado kaj aparatara akcelo.

Produktaj kategorioj

-

Telefono

-

Retpoŝto

-

WhatsApp

-

Skajpo

-

Skajpo

-

Skajpo