Unu-haltaj Elektronikaj Fabrikadaj Servoj, helpas vin facile atingi viajn elektronikajn produktojn de PCB kaj PCBA

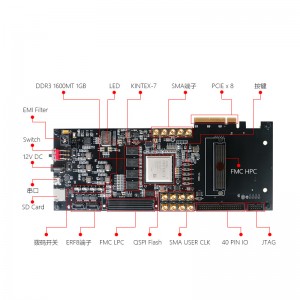

FPGA Xilinx K7 Kintex7 PCIe optika fibra komunikado

- DDR3 SDRAM: 16GB DDR3 64-bita buso, datumrapideco 1600Mbps

- QSPI-Fulmo: Peco de 128mbita QSPIFULMO, kiu povas esti uzata por FPGA-agordodosieroj kaj uzantodatumoj-stokado

- Interfaco PCLEX8: La norma interfaco PCLEX8 estas uzata por komuniki kun la PCIE-komunikado de la komputila bazcirkvito. Ĝi subtenas la normon PCI Express 2.0. La unu-kanala komunikada rapideco povas atingi 5 Gbps.

- Seria pordo USB UART: Seria pordo, konektebla al la komputilo per la miniUSB-kablo por plenumi serian komunikadon

- Mikro SD-karto: MikroSD-karto sidiĝas tute, vi povas konekti la norman MikroSD-karton

- Temperatursensilo: temperatursensila ico LM75, kiu povas monitori la median temperaturon ĉirkaŭ la disvolva tabulo

- FMC-etenda pordo: FMC HPC kaj FMCLPC, kiuj povas esti kongruaj kun diversaj normaj etendaj platkartoj

- ERF8 altrapida konekta terminalo: 2 ERF8-pordoj, kiuj subtenas ultra-altrapidan signalan transdonon 40-pinglan etendon: rezervita ĝenerala etenda IO-interfaco kun 2,54 mm 40-pinglan, efika O havas 17 parojn, subtenas 3,3 V

- La periferia konekto de la nivelo kaj la 5V-nivelo povas konekti la periferiajn flankaparatojn de malsamaj ĝeneraluzeblaj 1O-interfacoj

- SMA-terminalo; 13 altkvalitaj orumitaj SMA-kapoj, kio estas oportuna por uzantoj kunlabori kun altrapidaj AD/DA FMC-ekspansiokartoj por signalkolektado kaj prilaborado

- Horloĝa Administrado: Plurhorloĝa fonto. Ĉi tiuj inkluzivas la 200MHz sisteman diferencigan horloĝfonton SIT9102

- Diferenciala kristalo oscilanta: 50MHz kristalo kaj SI5338P programebla horloĝa administrada ĉipo: ankaŭ ekipita per

- 66MHz EMCCLK. Povas precize adaptiĝi al malsamaj uzhorloĝaj frekvencoj

- JTAG-pordo: 10 kudreroj 2,54mm norma JTAG-pordo, por elŝuto kaj sencimigado de FPGA-programoj

- Sub-restariga tensio-monitorada ĉipo: peco de ADM706R-tensio-monitorada ĉipo, kaj la butono kun la butono provizas tutmondan restarigan signalon por la sistemo

- LED: 11 LED-lumoj, indikas la elektroprovizon de la karto, signalon config_done, FMC

- Potenca indikilo, kaj 4 uzanto-LED-oj

- Ŝlosilo kaj ŝaltilo: 6 ŝlosiloj kaj 4 ŝaltiloj estas FPGA-rekomencigaj butonoj,

- Programo B butono kaj 4 uzantoklavoj estas kunmetitaj. 4 unu-tranĉila duobla ĵetŝaltilo

Skribu vian mesaĝon ĉi tie kaj sendu ĝin al ni

Produktaj kategorioj

-

Telefono

-

Retpoŝto

-

WhatsApp

-

Skajpo

-

Skajpo

-

Skajpo